Palm PCs: micro PC or macro failure? Pg 86

Howard Johnson loves voltage-regulator models Pg 22

**Issue 17**/2006

www.edn.com

HP-IB revolutionized ATE Pg 24

A tale about specs: Sometimes timing really is everything Pg 30

**Design Ideas** Pg 69

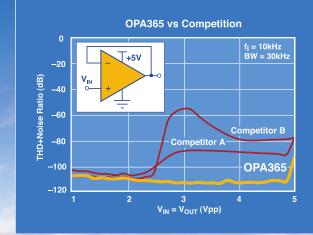

# Low Noise Low Distortion

### Zero-Crossover, 50MHz, Rail-to-Rail Amp

The OPA365 amplifier utilizes an innovative zero-crossover, single input stage architecture to deliver glitchless rail-to-rail performance with ultra-low distortion (0.0006% THD+N). Also featuring low noise (4.5nV $\sqrt{\text{Hz}}$ ) and high-speed operation (50MHz gain bandwidth), the device is ideal for a wide range of single-supply applications in portable instrumentation, data acquisition, audio, portable medical, test and measurement systems.

High Performance. Analog. Texas Instruments.

For datasheet and samples, visit

# Rated \*1 for Availability of Product!

Quality Components Just a Click Away!

1.800.344.4539 · www.digikey.com

\* New Product Added Daily!

# The Inside Edge that shapes the Future

Samsung Electro-Mechanics (Samsung) has started up production of **LEDs** for lighting as well as mobile phones, car navigators,

PMPs and Note PCs.

SB Byun (sbbyun@samsung.com, 949-797-8054)

Samsung has brought out 2, 3 Megapixel camera module with auto focus function.

JIM Park (jimpark@samsung.com, 847-549-9421)

Samsung has produced digital tuners compatible with all broadcasting signals worldwide, for TV, Set-top boxes and mobile phones,

as well as a variety of micro-sized RF components, **Bluetooth**, **wireless LAN**, **GPS Module**, **FEM**, etc., that support the portability of mobile devices.

### JS Han (han.jungsuk@samsung.com, 201-229-6096)

Samsung has completed development of world's first 0402(0.4X0.2mm) MLCC, as thin a human hair, which uses copper nickel, palladium as

internal electrode material. Specifically, 0402 Cu MLCC has better high frequency performance than others.

Peter Kang (semksk@samsung.com, 949-797-8017)

Samsung has offered multi-layer boards named, 'SAVIA™ (Samsung Any Via)', which have all-layer IVH characteristics and Flip Chip substrate.

Wes Sohn (wansohn@samsung.com, 480-592-0180)

SAMSUNG ELECTRO-MECHANICS

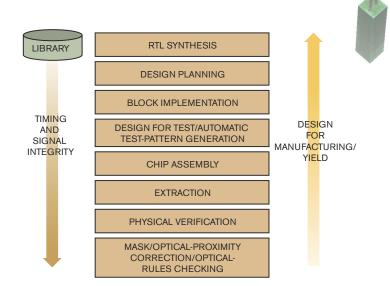

### Sifting the **DFM** players

With new DFM-tool companies popping up every month, it can be hard to select which you need for 65-nm processes. But the top three foundries at that node have made some of the choices for you. by Michael Santarini, Senior Editor

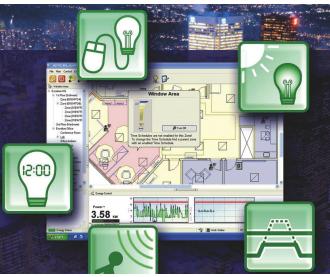

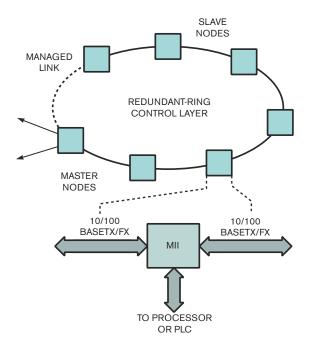

### **Smart-building** systems converge

As building-automation data flows onto enterprise networks and the Internet, designers are turning to integrated systems and Webbased services.

by Warren Webb, Technical Editor

# contents

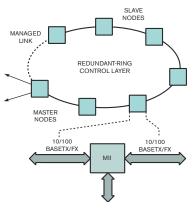

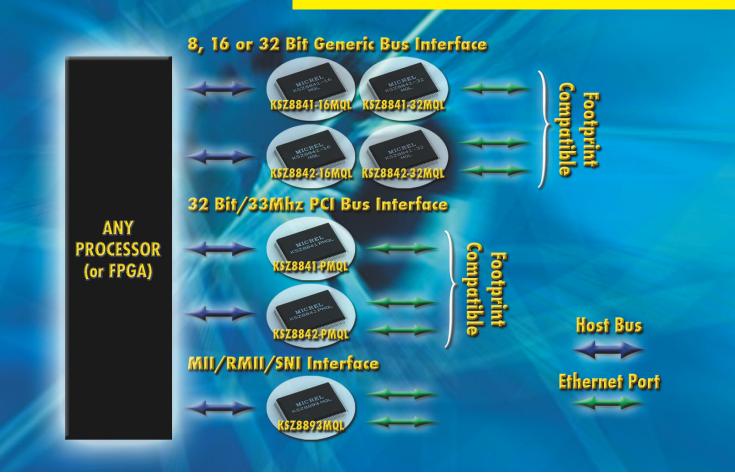

### **Designing Ethernet** into industrial applications

The right architectural decisions and careful implementation can help you meet your design goals. by Michael Jones, Micrel Inc.

### GNIDEAS

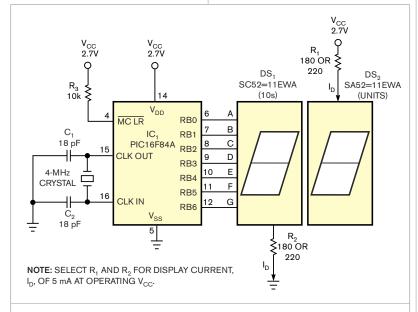

- 69 Ultralow-cost, two-digit counter features few components

- 70 Two-wire, four-by-four-key keyboard interface saves power

- 74 Gain-of-three amplifier requires no external resistors

- Send your Design Ideas to edndesignideas@reedbusiness.com.

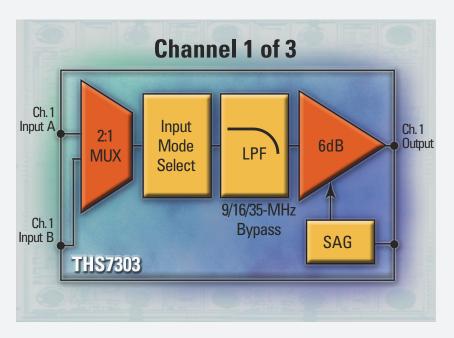

# 3-Ch. Low-Power Video Amp with I<sup>2</sup>C Control

The **THS73x3** family of high-performance video amplifiers from Texas Instruments provides the designer with unprecedented flexibility and control in configuring video systems without the need for hardware upgrades or modifications. Operating at 20x less power than competing amplifiers, these products are ideally suited for digital video systems like those incorporating TI's DaVinci™ and DLP® technologies.

|         | # of     | Filter -3 dB<br>Freq |       | Bypass<br>Bandwidth | Gain             | Input        | Output   | SAG    | Price<br>Starts |

|---------|----------|----------------------|-------|---------------------|------------------|--------------|----------|--------|-----------------|

| Device  | Channels | (MHz) (typ)          | Poles | (MHz) (typ)         | (dB)             | Coupling     | Coupling | Output | at 1K           |

|         |          |                      |       |                     |                  | AC-Bias,     |          |        |                 |

| THS7303 | 3        | 9, 16, 35            | 5     | 190                 | 6                | AC-STC,      | AC or DC | Yes    | \$1.65          |

|         |          |                      |       |                     |                  | DC, DC+Shift |          |        |                 |

|         |          |                      |       |                     |                  | AC-Bias,     |          |        |                 |

| THS7313 | 3        | 8                    | 5     | _                   | 6                | AC-STC,      | AC or DC | Yes    | \$1.20          |

|         |          |                      |       |                     |                  | DC, DC+Shift |          |        |                 |

|         |          |                      |       |                     | 0                | AC-Bias,     |          |        |                 |

| THS7353 | 3        | 9, 16, 35            | 5     | 150                 | 0,<br>Adjustable | AC-STC,      | AC or DC | No     | \$1.65          |

|         |          |                      |       |                     | Aujustable       | DC, DC+Shift |          |        |                 |

### **▶** Applications

- Set-top boxes

- Digital televisions

- Personal video/DVD recorders

- Portable USB devices

### **▶** Features

- 2.7V to 5V single-supply operation

- Low power consumption: 55mW at 3.3V

- 2:1 Input MUX allows multiple input sources

- I<sup>2</sup>C Control of all functions

- Integrated low-pass filters with 5th-order Butterworth characteristics

- Selectable input coupling modes

- Rail-to-rail outputs allow a variety of AC- or DC-coupled modes

- Individual channel disable with independent channel mute control

For Samples,

Evaluation Modules and

Technical Information

www.ti.com/ths7303 o 800.477.8924, ext. 13277

© 2006 TI

### contents 8.17.06

- 13 LabView celebrates 20th anniversary with new version, new features

- 13 Tiny board delivers Web connectivity

- 14 Lithography-savvy IC router circumvents third parties

- 16 Packet switching comes to backplanes

- 18 Research Update: Semiconductors, wireless SiGe transistors hit 500 GHz; Battery-free sensors convert motion into energy; Components, hardware, and interconnect webs of optical fiber see in all directions

- 20 Global Designer: India's Innoviti connects watches to wireless data; Research giant, vision expert collaborate on 3-D-chip-package research

### DEPARTMENTS & COLUMNS

- **EDN.comment:** Editorial ethics: meeting the ASBPE's transparency mandate

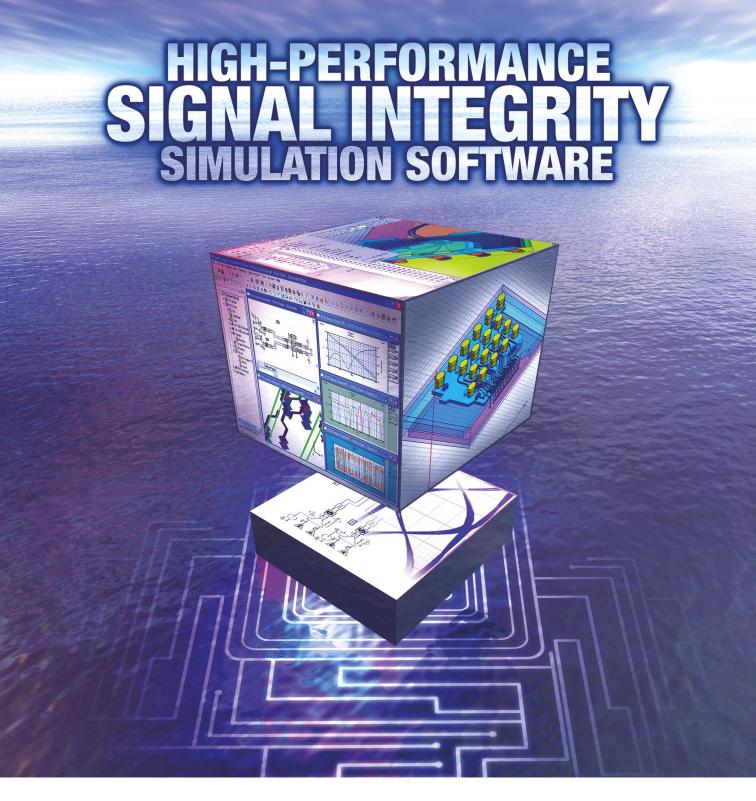

- Signal Integrity: Voltage-regulator model

- 24 Milestones That Mattered: HP-IB revolutionized ATE: Designers benefited from smarter connected instruments

- 30 Tales from the Cube: Specs: Sometimes timing really is everything

- 86 Reality Check: Palm PCs: micro PC or macro failure?

- Switches and Relays: Self-protected electronic fuses, switch catalog and CD-ROM, USB 2.0 switches, SPDT analog switches, and more

- Microprocessors: Upgrade for Windows Mobile 5.0, hydraulic-control systems, multimedia starter kits, and more

- 83 EDA Tools: IC tools with I/O sequencing and integrated-design environment with hierarchical database

EDN ® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDIN @ copyright 2006 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year, Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6.J3. E-mail: subsmail@reedbusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 51, Number 17 (Printed in USA).

# MAKE SURE TO CHECK THE EXPIRATION DATE ON THE LANGUAGE YOU PLAN TO USE.

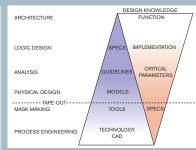

INTEGRATED SYSTEM DESIGN + DESIGN FOR MANUFACTURING + ELECTRONIC SYSTEM LEVEL DESIGN + FUNCTIONAL VERIFICATION

Functional Verification | If you buy a loaf of bread and it goes bad, so what? You're out a loaf of bread. Buy into a verification tool using a single-vendor language like Vera or "e" and you're in for trouble. Questa," Mentor Graphics' advanced functional verification platform, is the industry's most comprehensive solution, and offers you all of the new, standard verification like SystemVerilog, PSL and SystemC. So if you're doing coverage-driven verification, transaction-level verification or using assertions, choose a solution that will stay fresh for years. Go to www.mentor.com/questa or call 800.547.3000.

# EDN )

# online contents

### ONLINE ONLY

Check out these Web-exclusive articles:

Consumer Court: HSDPA phone, 200-Mbps power-line adapter, more ...

Snap judgments on new digital-consumer

www.edn.com/article/CA6354460

### Power-line networking demands holistic design

Design Decisions: SiConnect finds that implementing a "simple" chip architecture can be anything but.

www.edn.com/article/CA6355490

### Panel maps issues for process-node change

A panel held in conjunction with the Design Automation Conference explored one of the most complex decisions facing chip-design managers today: choosing the right time to move on to the next process node.

www.edn.com/article/CA6357237

### Managers offer tales of consumer SOC design

Three seasoned design managers offer concrete advice on managing a successful complex chip design for the challenging consumer-electronics market.

www.edn.com/article/CA6356787

### DFM's hot, ESL's a ways away

Chief technology officers from major companies discuss the continuing battle for yield and the continuing wait for electronicsystem-level tools.

www.edn.com/article/CA6355935

### READERS' CHOICE

Recent articles getting high traffic on www.edn.com:

Is chip design different after 90 nm?

www.edn.com/article/CA6347251

### Design Idea: Microprocessor generates programmable clock sequences

www.edn.com/article/CA6351286

### Design Idea: Tapped inductor, boost regulator deliver high voltage

www.edn.com/article/CA6351288

### 32-nm CMOS begins to take shape

www.edn.com/article/CA6355048

### Immersion-lithography road map hits dead end

www.edn.com/article/CA6355060

### 100-Mbps broadband: how, why, when, and where?

www.edn.com/article/CA6347250

### MP3 disassembly: tech for thrifty tune-toters

www.edn.com/article/CA6347256

### Reducing ground bounce in dc/dcconverter applications

www.edn.com/article/CA6347258

### Friend or foe: Battery-authentication ICs separate the good guys from the bad

www.edn.com/article/CA6301616

### MICROPROCESSOR **DIRECTOR**

- www.edn.com/microdirectory

- Technical details on every processor family from more than 60 companies

- Ability to filter based on your target application

- Exhaustive parametric tables

- More than 120 block diagrams

- Expanded analysis of each company and its offerings

### ARE YOU IMPATIENT?

Use the following shortcuts to quickly reach the EDN content you want.

### Design Ideas

→ www.edn.com/designideas

### Prying Eyes

→ www.edn.com/pryingeyes

### Tales From The Cube

→ www.edn.com/tales

### Voices

→ www.edn.com/voices

### Milestones That Mattered

www.edn.com/milestones

### News and new products

→ www.edn.com/news

### Technical features

www.edn.com/features

### Columnists

www.edn.com/columnists

### BY MAURY WRIGHT, EDITOR IN CHIEF

# Editorial ethics: meeting the ASBPE's transparency mandate

just got back from a trip that included two days at the ASBPE (American Society of Business Publication Editors) National Editorial Conference, at which editorial-ethics issues were hot topics. At the conference, the ASBPE (www.asbpe.org) unveiled its *Guide to Preferred Editorial Practices*. A mandate for "ethics-guide transparency" appears on the first page of the guide, and speakers at the conference stressed this subject. The guide states, "ASBPE urges publishers and editors to make their ethical standards transparent both for its internal staff and externally for its readers, advertisers, and others in their markets." Although *EDN* operates with high regard for ethics, I'm not sure that we've ever explicitly defined our policies to you, the readers, so here goes.

A couple of years ago, our parent company, Reed Business, formally adopted the ASME (American Society of Magazine Editors) Guidelines (www.magazine.org/editorial/guidelines). Reed Business stipulates that all publi-

### **EDN's AZBEE WINS**

- Gold Award, Regular Department: "Prying Eyes," *EDN*, June 9, 2005 (www.edn.com/article/CA605509), July 7, 2005 (www.edn.com/article/CA621643), and Aug 4, 2005 (www.edn.com/article/CA629314).

- Bronze Award, Computer Generated Front Cover: "Who are you buying your EDA software from?" EDN, Aug 18, 2005 (www.edn.com/toc-archive/2005/ 20050818.html).

- Bronze Award, Publication Redesign: "Song Wars," EDN, June 9, 2005 (www.edn.com/tocarchive/2005/20050609.html.

cations must abide by the ASME document. We also have an internal editorial board that both augments ASME and watches over the actions of our titles. *EDN* may also adopt or follow the ASBPE guide in areas that the ASME doesn't cover and vice versa.

I'd like to briefly highlight a few details that are important for EDN to earn your trust as a source of information. At the highest level, we simply never consider who advertises when we write features, columns, new products, or any other type of article. But we take additional steps to ensure that there is no illusion of collusion. For example, we never allow an advertiser to buy an ad opposite an editorial mention. A vendor might know that one of its engineers has a bylined article scheduled for an upcoming issue, but we don't allow that vendor to place an ad in the pages of that contributed article. The only reason that you might in some instances see an ad adjacent to an editorial mention would be that the vendor had previously contracted for the same "position" in each issue or every other issue. For example, an advertiser could buy a position in the Pulse section. On occasion, a Pulse article might mention that advertiser.

We also seriously consider the issues of our masthead and staff. Some publications list freelance or contract writers as if they were staff members. ASME mandates that we convey the titles only of full-time staff. We identify any contractors as "contributing editors." Some publications also use staff editors to write advertiser-sponsored content, such as supplements and advertorials; however, we don't allow our staff members to work on projects wherein an advertiser dictates the content.

We are also careful about accepting benefits, such as paid travel from vendors or trade associations. Vendors frequently offer to pay for airfare and hotel accommodations for an *EDN* editor's visit. We don't accept such offers when the vendor makes them only to *EDN*. We sometimes accept travel reimbursement when a company offers travel to *EDN* and broadly to all of our competitors. At the ASBPE conference, however, I learned that we should disclose the acceptance of reimbursement in any article that eventually evolves from such a trip.

The same rules that apply to our magazine apply to our Web site, e-mail newsletters, and any other media that we use. The online area is one in which some publishers are loosening their ethics policies. Please contact me if you ever think we've failed to live up to our ethics commitment. I want to know.

Also at the ASBPE conference, *EDN* picked up some ASBPE National Azbee awards for magazines with circulation of more than 80,000 readers (see **sidebar** "*EDN*'s Azbee wins").**EDN**

You can reach me at 1-858-748-6785 or mgwright@edn.com.

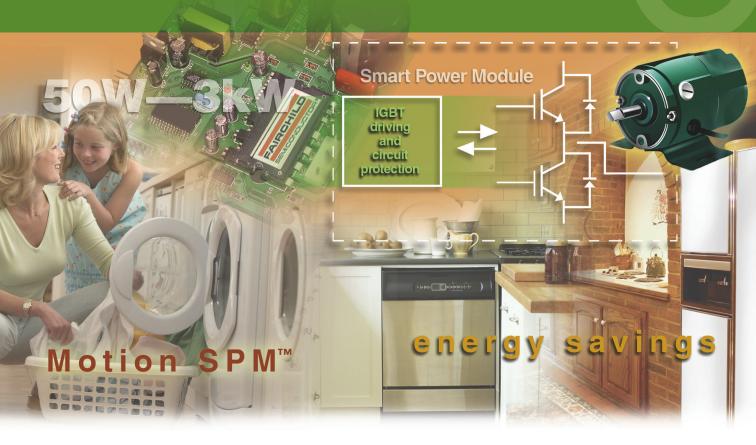

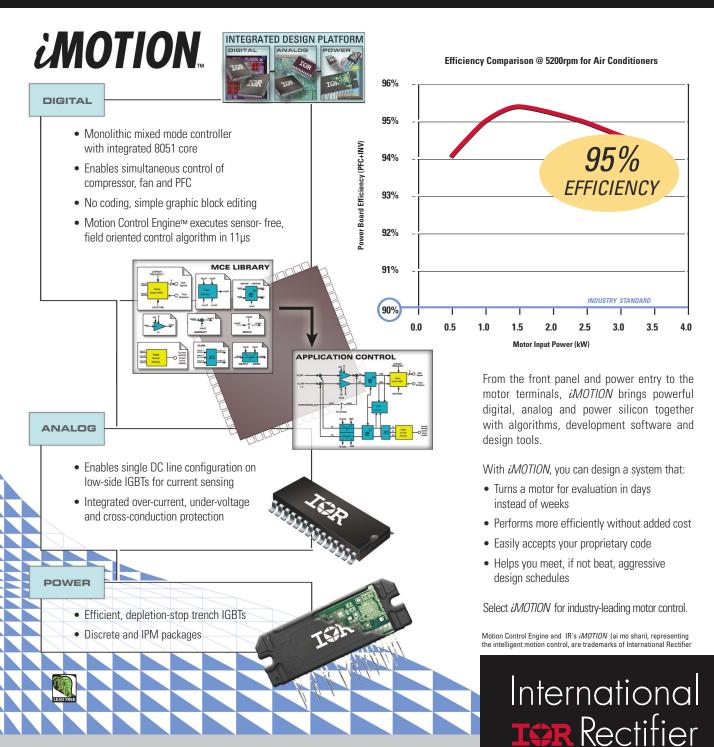

# Inverter motor designs: half the energy, cost and time.

### Meet energy usage regulations with SPM

Satisfy government energy requirements for home appliances with Fairchild's Smart Power Modules (SPM) for variable speed motor drives. One highly integrated package, with up to 16 discrete components, provides space savings, ease-of-use and greater reliability.

Our SPM portfolio covers inverter motor designs from 50W to 3kW, all with adjustable switching speeds, superior thermal resistance and low EMI. We're also the only company to offer a module for partial PFC switching converters.

Smart Power Modules: where energy is critical, SPM is there.

For more information on our SPM products, evaluation boards, and all of our design tools, visit www.fairchildsemi.com/spm.

Fairchild Smart Power Modules are the optimal solution for variable speed motor drives in home appliance designs.

# EXPRESSION DE PERFORMANCE...

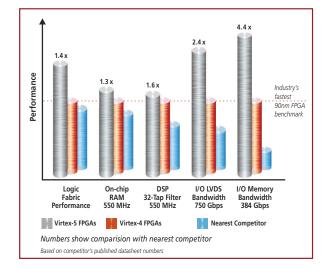

Achieve highest system speed and better design margin with the world's first 65nm FPGAs.

Virtex<sup>™</sup>-5 FPGAs feature ExpressFabric<sup>™</sup> technology on 65nm triple-oxide process. This new fabric offers the industry's first LUT with six independent inputs for fewer logic levels, *and* advanced diagonal interconnect to enable the shortest, fastest routing. Now you can achieve 30% higher performance, while reducing dynamic power by 35% and area by 45% compared to previous generations.

### Design systems faster than ever before

Shipping now, Virtex-5 LX is the first of four platforms optimized for logic, DSP, processing, and serial. The LX platform offers 330,000 logic cells and 1,200 user I/Os, plus hardened 550 MHz IP blocks. Build deeper FIFOs with 36 Kbit block RAMs. Achieve 1.25 Gbps on all I/Os without restrictions, and make reliable memory interfacing easier with enhanced ChipSync™ technology. Solve SI challenges and simplify PCB layout with our sparse chevron packaging. And enable greater DSP precision and dynamic range with 550 MHz, 25x18 MACs.

Visit www.xilinx.com/virtex5, view the TechOnline webcast, and give your next design the ultimate in performance.

The Ultimate System Integration Platform

### PUBLISHER, EDN WORLDWIDE

### John Schirmer

1-408-345-4402; fax: 1-408-345-4400; jschirmer@reedbusiness.com

### EDITOR IN CHIEF

Maury Wright 1-858-748-6785; mgwright@edn.com

### EXECUTIVE EDITOR

Ron Wilson 1-408-345-4427; ronald.wilson@reedbusiness.com

### MANAGING EDITOR

Kasey Clark 1-781-734-8436; fax: 1-781-290-3436; kase@reedbusiness.com

### EXECUTIVE EDITOR, ONLINE Matthew Miller

1-781-734-8446; fax: 1-781-290-3446; mdmiller@reedbusiness.com

### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

### EMBEDDED SYSTEMS

Warren Webb, Technical Editor; 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

### ANALOG

Paul Rako, Technical Editor; 1-408-745-1994; paul.rako@reedbusiness.com

### EDA, MEMORY,

### PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor; 1-408-345-4424; michael.santarini@reedbusiness.com

### MICROPROCESSORS, DSPs, TOOLS

Robert Cravotta, Technical Editor; 1-661-296-5096; fax: 1-781-734-8070; rcravotta@edn.com

### MASS STORAGE, MULTIMEDIA.

PCs AND PERIPHERALS

Brian Dipert, Senior Technical Editor;

1-916-760-0159; fax: 1-781-734-8038;

### bdipert@edn.com POWER SOURCES,

### ONLINE INITIATIVES

Margery Conner, Technical Editor; 1-805-461-8242; fax: 1-805-461-9640; mconner@connerbase.com

### DESIGN IDEAS EDITOR

Brad Thompson edndesignideas@reedbusiness.com

### SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-734-8439;

rances I Granville, 1-781-734-843 fax: 1-781-290-3439; f.granville@reedbusiness.com

### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-347-9605; mbutler@reedbusiness.com

### EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager

1-781-734-8445; fax: 1-781-290-3445

Steve Mahoney, Production/Editorial Coordinator

1-781-734-8442; fax: 1-781-290-3442

Melissa Annand, Newsletter/Editorial Coordinator

Contact for contributed technical articles

1-781-734-8443; fax: 1-781-290-3443

Adam Odordi, Prepress Manager

1-781-734-8325; fax: 1-781-290-3325

### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

### COLUMNISTS

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn

### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Brashears, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086

Pam Boord, Advertising Art 1-781-734-8313; fax: 1-781-290-3313

### **EDN EUROPE**

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirlimaya Varma, Editor in Chief kirli.varma@rbi-asia.com

### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.jp Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

### DENNIS BROPHY

Director of Business Development Mentor Graphics

### DANIS CARTER

Principal Engineer, Tyco Healthcare

### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

### DMITRII LOUKIANOV

System Architect, Intel

### RON MANCINI

Engineer

### GABRIEL PATULEA Design Engineer, Cisco

MIHIR RAVEL

VP Technology, National Instruments

### DAVE ROBERTSON

Product Line Director, Analog Devices

### SCOTT SMYERS

VP Network and System Architecture Division, Sony

### TOM SZOLYGA

Program Manager, Hewlett-Packard

### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax: 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@readbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

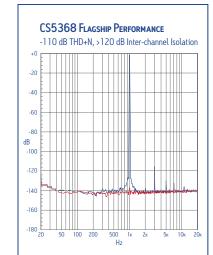

# NI Scopes High Performance to Low Cost

National Instruments offers a full range of PCI and PXI digitizers/PC-based oscilloscopes, including the multiple-award-winning NI PXI-5922 flexible-resolution digitizer – the highest-resolution digitizer on the market.

### PCI and PXI Digitizers/ PC-Based Oscilloscopes

| Description                                             | Resolution (bits) | Sampling<br>Rate |

|---------------------------------------------------------|-------------------|------------------|

|                                                         | 24                | 500 kS/s         |

|                                                         | 22                | 1 MS/s           |

| User-defined resolution                                 | 20                | 5 MS/s           |

|                                                         | 18                | 10 MS/s          |

|                                                         | 16                | 15 MS/s          |

| High resolution,                                        | 14                | 100 MS/s         |

| high speed                                              | 12                | 200 MS/s         |

| Digital downconverter (DDC), alias-protected decimation | 14                | 100 MS/s         |

| Low cost, high speed                                    | 8                 | 250 MS/s         |

| Low cost, mgn speed                                     | 8                 | 100 MS/s         |

OEM pricing, customization, and support available.

To view an online demo of the PXI-5922 flexible-resolution digitizer, visit ni.com/oscilloscopes.

800 891 8841

© 2006 National Instruments Corporation. All rights reserved.

National Instruments, NI, and in.com are trademarks of

National Instruments. Other product and company names listed

are trademarks or trade names of their respective companies.

7482-101

THINK Wireline and Wireless ICs.

THINK Seamless Communications.

THINK Infineon.

OUR MISSION is to help your customers achieve seamless communications.

Count on Infineon to deliver the architectural building blocks.

AT INFINEON, we never stop thinking about end-to-end semiconductor solutions. Our broad portfolio in wireline and wireless technology enables us to deliver innovations that help you build tomorrow's converged networks. In wireline, we lead the way in broadband access, CPE, core access and VoIP system-on-chip products. In wireless, we're number one in RF technologies with the solutions you need from 2G, 3G, WLAN to an entire line of flexible mobile phone platforms including entry phones, feature phones and mobile software solutions. We also provide complete solutions, including application software and ready-to-use platforms, to help you get to market faster.

WHEN YOU think about seamless communications, turn to the company that delivers tomorrow's wireline and wireless innovations. Think Infineon.

www.infineon.com/us/comm

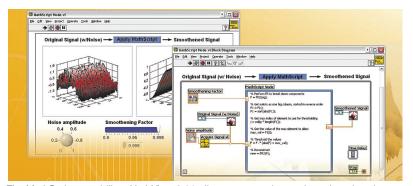

### LabView celebrates 20th anniversary with new version, new features

he lifetime of successful programming languages is approximately 50 years, according to James Truchard, PhD, co-founder, chairman, and chief executive officer of National Instruments. That's an amazing amount of time in this era of product lifetimes that are typically months rather than years. NI's flagship product, LabView, an application-development environment that embodies its own graphical-programming language, is now 20 years old. In honor of that milestone, NI is announcing Version 8.20 and is looking at LabView's future path for the next 30 years. Although LabView doesn't try to be all things to all people and is not as ubiquitous as applications such as word processors and general-purpose spreadsheets, it continues to spread its wings wider to support an ever-broadening spectrum of applications in engineering and science. The software has a diverse range of capabilities and uses, most notably now including system-level EDA, embedded-system development, and FPGA-based rapid prototyping, and the user base continues its high regard for the package's ease of use.

Among the key additions to Version 8.20 is MathScript, which allows algorithm development in such text-based third-party packages as the MathWorks' (www.math works.com) Matlab and Comsol's (www. comsol.com) Comsol Script. Version 8.20 also supports object-oriented programming with the ability to create classes and objects; encapsulate data and methods; define methods as public, private, or protected; and more. This version also improves on LabView's control-system-development capabilities with, among other upgrades, a 14-times speed increase in

execution of PID (proportional-integral-derivative) algorithms. LabView lets you take advantage of multicore CPUs, which are rapidly becoming standard in PCs. Orderof-magnitude execution-speed improvements are common when you move LabView applications from conventional processors to dual-core units. Prices for LabView start at \$1199.

-by Dan Strassberg National Instruments, www.ni.com.

The MathScript capability of LabView 8.20 allows you to write text-based routines in third-party languages and incorporate the routines within LabView block diagrams.

### Tiny board delivers Web connectivity

A frequent design-retrofit task is to add network connectivity to stand-alone embedded controllers or handheld instruments. Targeting these efforts, Mosaic Industries recently announced the Ethersmart Wildcard, a 2×2.5-in. expansion board that allows application programs to send e-mails, transmit data, or alert other computers on the network when significant events occur. The company based the board on the Lantronix (www.lantronix.com) Xport, which combines an x86 processor, flash memory, a 10/100-Mbit Ethernet network-interface controller, and an RJ-45 jack.

An onboard UART buffers data between the Xport and the host controller. The Ethersmart Wildcard im-

The Ethersmart Wildcard Webenables stand-alone instrumentation to remotely monitor status, diagnose problems, or update software.

plements multiple Web protocols to establish and manage communications. Precoded software allows applications to compose and send e-mail, establish a TCP/IP (Transfer Control Protocol/Internet Protocol) connection to exchange data, and accept connections from a Web browser to serve dynamic Web pages in response to queries. The Ethersmart Wildcard is now available and sells for \$140 (100).-by Warren Webb ▶ Mosaic Industries Inc, www.mosaic-industries.com.

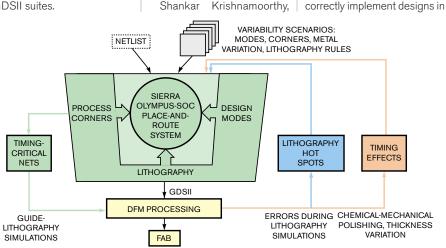

### Lithography-savvy IC router circumvents third parties

hysical-IC designers now have an alternative to Cadence (www. cadence.com), Synopsys (www. synopsys.com), and Magma (www.magma-da.com) physical-design flows: Sierra Design Automation's new detailed-router tool. The router joins the company's Pinnacle, a combination floorplanner, physical-synthesis, and clocktree-synthesis tool. The new tool, the Olympus-SOC (system-on-chip) netlist-to-GDSII (Graphic Design System II) suite, competes directly with Cadence's Encounter, Synopsys' IC Compiler and Magma's Blast and new Talus RTL-to-GDSII suites.

Pinnacle supports multimode design, in which ICs have, for example, off, lowpower, standby, and full-performance modes. It is becoming common for advanced-IC designs to have several blocks, each of which can operate in multiple modes. Thus, designers need to account for multiple combinations of mode switching. Pinnacle users can check the impact of multimode and multiprocess corners on timing, power, and signal integrity, but the availability of Olympus eliminates the need to pass that information to a third-party detailed router.

Shankar Krishnamoorthy,

chief technology officer of Sierra, says that there hasn't been a significant breakthrough in routing since Magma introduced Blast about eight years ago. Routing needs have evolved, he says, and GDSII netlists now have to accurately account for not only DRC (design-rule checking), but also lithography. "We've been developing this router for the last two years and working closely with our customers' lithography groups to understand the issues they see with the layouts passed to them," says Krishnamoorthy. He notes that, whereas most DFM (design-for-manufacturing) start-ups focus on analysis or finding DFM problems, more tools are necessary to help fix the problems or to

the first place. "Finding the problem is probably a quarter of the solution," says Krishnamoorthy. "At 65 and 45 nm, the number of manufacturing faults is going to be so great, you need to move into the implementation phase, so that you are producing designs that are correct by construction rather than reacting to something that is broken."

The new router is a hybrid technology that uses engines with and without grids. Krishnamoorthy says that the tool stays on the grid for most routes but directs traces off the grid to make connections to vias, for example, to avoid creating unnecessary notches that can degrade performance or cause failures in lithography. Whereas most routers target line and spacing rules, the Sierra router focuses on geometric patterns and automatically flags and fixes routing situations that are lithographically incorrect. These situations include pinching, bridging, overlap, and minimum-space and -width violations. The tool also has a DRC engine to ensure that the targeted process rules are guiding the routing, as well. The DRC engine isn't of sign-off quality, so you still need a third-party DRC/LVS (layoutversus-schematic) tool for final verification.

Users feed the Sierra Olympus-SOC system a synthesized netlist and variability scenarios describing modes, corners, on-chip variation, metal variation, and lithography rules. The tool then works with thirdcritical-area-analysis, simulation, and timing tools to route the design.

-by Michael Santarini Sierra Design Automation, www.sierra-da.com.

The Olympus-SOC router focuses on geometric patterns and automatically flags and fixes routing situations that are lithographically incorrect.

### **DILBERT** By Scott Adams

### **EPIC Solutions for Real World Problems**

# Rugged, Reliable, and Ready-to-go

Based on the Embedded Platform for Industrial Computing (EPIC), the EPX-C3 combines the processor and I/O functions required for medical, transportation, instrumentation, communication, MIL/COTS, security, and other demanding applications.

- Fanless 733MHz C3 Processor

- Up to 2GB Flash memory

- 4x AGP CRT/LCD controller

- 10/100 Mbps Ethernet

- USB 2.0 support

- 4 COM channels

- 24 Digital I/O lines

- EIDE, FDC, and Kybd controllers

- PC/104 & PC/104-Plus expansion

- -40°C to +85°C operation

- Size: 4.5" x 6.5" (115mm x 165mm)

- Quick Start Developers kits for Windows® XP, CE, and Linux

Profit from our proven experience. We look forward to the opportunity to demonstrate how our success in the industrial market can work for you.

Call 817-274-7553 or Visit www.winsystems.com Ask about our 30-day product evaluation!

0000000000000

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

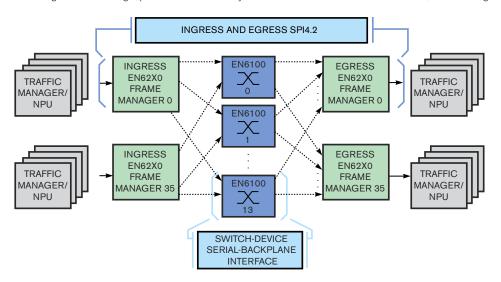

# Packet switching comes to backplanes

y looking at switching equipment, you'd never know that the trend in the communications and networking world is toward TCP/ IP (Transfer Control Protocol/ Internet Protocol). Once packetized data enters a line card and passes through a trafficmanager ASIC or NPU (network-processing unit), it almost universally emerges onto the backplane as fixed-length cells, rather than as packets. Such is the lingering legacy of ATM (asynchronous-transfer mode), or, if you have a longer memory, of ISDN (Integrated Services Digital Network).

Serious inefficiencies occur in the communication between variable-length packets and fixed-length cells, however. Each cell must have a header. And, as the network schedules, prioritizes, and divides packets into cells, these headers, along with the inability to fill all the cells, can lose as much as 50% of the data bandwidth, according to Robert Sturgill, president

and chief executive officer of start-up Enigma Semiconductor. Sturgill may be biased, however, because Enigma has just announced an alternative approach: a family of scheduling and switching chips that

In byte-aligned transmission, nearly head-to-tail packets stream through a switching fabric.

moves variable-length packets across backplanes at the kinds of speeds today's metropolitan-area-network edge routers and multiservice switches demand

Sturgill says that switching packets across the backplane poses formidable problems. You must concatenate packets with little dead time between them. Otherwise, the resulting efficiency is worse than for a

cell-based switching system. And the shared-memory architectures for packet switching scale well only up to the limits of the memory chips for implementing those architectures.

With these problems in mind, Enigma developed a fabric manager employing an algorithm that relates to SONET (synchronous-optical-network) virtual concatenation. In this approach, "byte-aligned transmission," nearly head-to-tail packets stream through a switching fabric. Combining this idea with an exhaustively tested on-the-fly scheduling algorithm and a lightweight packet header produces a system architecture that reaches 98% efficiency, according to the company's simulations. Meanwhile, the new fabric attacks the problem of scalability by abandoning the sharedmemory approach, instead employing full crossbar switches. Adding switch chips linearly expands the fabric's bandwidth.

For implementation, Enigma's designers employed a two-chip approach using TS-MC's 130-nm, low-voltage

process. The first chip, the fabric manager, resides on the line cards and connects to four SPI 4.2 streams to and from traffic managers or NPUs. The chip prioritizes packets according to qualityof-service request tags, attaches their headers, and concatenates them into an outgoing stream toward the fabricor vice versa for traffic moving in the other direction. The proprietary prioritization scheme provides for eight classes of service. According to Enigma's vice president of marketing, lan Ferguson, the device can also dedicate some links to handle either switched-network traffic or video-over-Internet Protocol and similar payloads. The chip includes a significant amount of on-chip memory to eliminate the cost and space of using off-chip RAM on the line card.

To connect the fabric manager to its fabric, Enigma employs the ABP (Advance Backplane) physical-layer technology from Rambus (www.rambus.com), allowing a speed of 12.5 Gbps per link between line cards and the backplane. The availability of a variety of codecs permits designers to choose a trade-off point for raw speed versus reliability.

The second chip, the EN-61xx crossbar switch, integrates as many as 36 ABPlinks per chip and can reach an aggregate throughput of 360 Gbps of nonblocking, full-duplex traffic. The devices will be available in a range of sizes ABP-link maximum and speeds. The company expects to have both chips, the supporting system-level simulation, and the modeling tool available for sampling month.-by Ron Wilson

**⊳Enigma**, www.enigma.com.

Enigma's fabric manager and crossbar-switch chips schedule and switch complete packets across backplanes using links operating as fast as 12.5 Gbps.

Design Reuse

Board Integration HW/SW Partitioning

## Think Embedded? Peripherals

**Need to Customize Verification**

Custom Instructions Multi-Core Design

Get There First

When it's time to design your next embedded system, think Altera. Use our FPGAs for coprocessing or peripheral expansion for your CPU. Or use our Nios<sup>®</sup> II soft-core processor to quickly create your own stand-alone custom microcontroller. Either way, Altera offers the flexibility to improve your team's productivity and time-to-market while lowering system cost and reducing the risk of obsolescence.

If you're thinking of your next embedded design, think FPGAs—think Altera.

- World's top 20 electronic OEMs are already using Altera embedded solutions

- Over 15,000 Nios II licenses worldwide

- Support for industry-standard tools and operating systems

The Programmable Solutions Company®

www.altera.com

### RESEARCH UPDATE BY MATTHEW MILLER

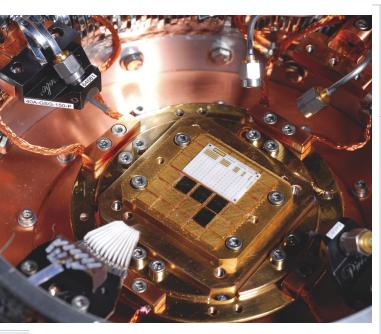

### Semiconductors, wireless SiGe transistors hit 500 GHz

A team of researchers from IBM and the Georgia Institute of Technology has demonstrated SiGe (silicon-germani-

um), heterojunction, bipolar transistors operating at more than 500 GHz. Although the group used liquid helium to

SiGe-based chips (black squares) sit inside a cryogenic test station, where they demonstrated speed of 500 GHz when cooled to 4.5K (courtesy Georgia Institute of Technology).

cool the transistors to 4.5K (-451°F) to obtain the result, the same devices operated at 350 GHz at room temperature, and better-optimized transistors could approach terahertz room-temperature rates, according to the research team.

IBM fabricated the test devices on a prototype, fourth-generation SiGe process using 200-mm wafers and an older, nonoptimized mask set. The speed record suggests that SiGe may be able to perform beyond the performance limits scientists presume under current theory; the group's next task is to explain the physics behind the better-than-expected performance.

▶ Georgia Institute of Technology, www. gatech.edu.

**▶IBM,** www.ibm.com.

### Battery-free sensors convert motion into energy

MicroStrain has won a US Navy contract to develop wireless strain sensors that can operate indefinitely thanks to their ability to harvest energy from the rotating helicopter components on which they are installed.

The piezoelectric components generated approximately 1 mW in tests simulating straight, level flight and approximately 5 mW in simulations of maneuvers such as hard climbs and gunnery turns. The sensors, used to monitor strain for monitoring fatigue and estimating component life, consume 0.9 mW while sampling 40 times/sec and transmitting their findings as far as 70m, according to the company.

**►MicroStrain**, www. microstrain.com.

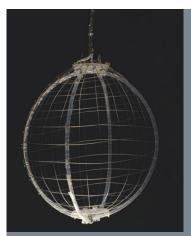

MIT researchers built a spherical arrangement of optical fibers that senses the direction, intensity, and phase of incoming light (courtesy Greg Hren, MIT).

# Components, hardware, and interconnect webs of optical fiber see in all directions

Researchers at the Massachusetts Institute of Technology have fashioned a web of optical fibers into an optical system that boasts potentially useful advantages over conventional 2-D lenses or detectors.

The 1-mm-thick fibers feature a glass core that has metal electrodes running along its length and is encased in a transparent, polymer insulator. When researchers weave these fibers into a spherical shape, they constitute an optical system that—with the help of a computer for interpretation—can detect the direction, intensity, and phase of incoming light.

Unlike conventional lenses, which are limited to the view along a certain axis, the fiber spheres can sense light all around them. The researchers cite flexibility, durability, and low weight as other advantages of the technology over conventional lenses. A densely woven fabric of smaller diameter fibers could one day enable visually aware clothing for soldiers or people with sight impairments, according to the MIT team.

Massachusetts Institute of Technology, www.mit.edu.

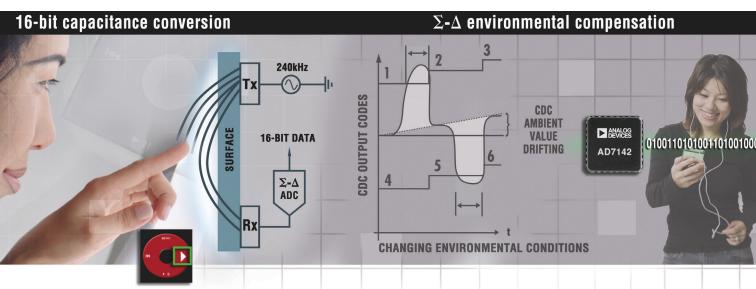

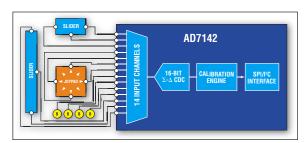

# 16-bit touch controller for the best user experience. In data conversion, analog is everywhere.

### 16-bit $\Sigma$ - $\Delta$ CDC ...

- <1 femtofarad resolution</li>

- Full power mode: <1 mA

- Low power mode: 50 μA

- Shutdown current: <2 μA

- Supply voltage: 2.6 V to 3.6 V

- Automatic environmental calibration

- Automatic adaptive sensitivity

- SPI® or I2C® interface

- 32-lead 5 mm imes 5 mm LFCSP

- Price: \$1.65 (1k quantities)

### ... enabling multiple applications

- · Consumer electronics

- · Medical instrumentation

- · Automotive applications

- · Industrial equipment

- · PC peripherals

With 14 inputs, the AD7142 can be programmed for a variety of navigation functions including buttons, sliders, scroll wheels, and joypads.

### Improved sensitivity and environmental calibration—made possible by $\Sigma$ - $\Delta$ conversion

For products with increasing feature convergence, finger-driven navigation enhances the user experience—for designers as well as consumers. The AD7142 capacitance-to-digital converter (CDC) with on-chip environmental compensation delivers unmatched touch control performance. It offers:

- · Reliable performance over supply and temperature

- · Programmable functionality and touch sensitivity

- 50% lower power than competitive solutions

- Development tools, such as reference designs and host software, that reduce time to market

ADI also offers CDC solutions for measuring proximity, position, level, pressure, and humidity.

### New online seminar:

View the "Innovative Human Interface Design Techniques Using CDCs" seminar at <a href="https://www.analog.com/onlineseminar-CDC">www.analog.com/onlineseminar-CDC</a>.

### **AGLOBAL DESIGNER**

# India's Innoviti connects watches to wireless data

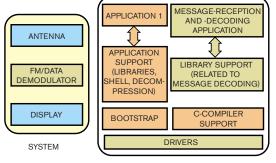

angalore start-up Innoviti Embedded Solutions has developed a two-chip, wireless product that enables wrist watches to receive personalized messages and news feeds. One chip performs the RF-reception tasks, and the second controls other functions, including timekeeping, power management, and display.

The RF chip operates in the FM band of 88 to 108 MHz and uses the excess bandwidth available in commercial FM-radio-transmission streams to send data as a subcarrier. This approach enables data to coexist with the radio transmission and allows radio stations to use their infrastructure to provide value-added services. The company based the controller chip on an 8051 core, and the device has a two-cycle execution with power-efficient modes.

The main challenges in designing the product were controlling power consumption and cramming the package into a small profile to fit into a

typical watch case. Because RF reception usually results in high power consumption, the designers implemented reception in time slots that synchronize with the transmitting server to cut power demand. The watch uses an OLED (organic-LED) display in place of more common LCDs to reduce power consumption. OLEDs are power-efficient and slim, and they provide high visibility, even in low-lighting conditions.

The size constraint for the design was less than 6 mm for the combined electronics, display, and battery. "One of the toughest challenges in the entire design was the antenna design. At 100 MHz, the wavelength is 3m, so an efficient antenna design would require at least 75m³ of space," says Ashok Baragi, Innoviti's vice president of engineering. "We had to figure out how to use the watch's internal mechanical features to create an antenna"

For power, the watch uses a lithium-ion battery because it

SOFTWARE

Innoviti's two-chip, wireless product enables wrist watches to receive personalized messages and news feeds. The design separates the software architecture from the hardware interfaces to provide for easy layering—without affecting power consumption.

# The challenge was to abstract the software architecture from the hardware interfaces.

provides a high capacity in a small form factor. However, watch manufacturers may switch to lithium-polymer varieties because manufacturers can fabricate them in different shapes to cater to various watch profiles.

Sophisticated built-in software enables the watch to perform its data-reception tricks. The challenge was to abstract the software architecture from the hardware interfaces to provide for easy layering without adversely affecting power consumption. A lean core kernel with a simple scheduler manages the hardware interfaces. The scheduler synchronizes with the transmitter, which runs on an independent clock, using a network-timing reference that transmits to the receiver.

A leading watch manufacturer is currently evaluating Innoviti's design for commercialization but has not announced a schedule for public availability of a watch based on this technology.

-by Chitra Giridhar, EDN Asia

▶Innoviti Embedded Solutions, www.innoviti.com.

# Research giant, vision expert collaborate on 3-D-chippackage research

With products ranging from handsets to MP3 players to industrial-control systems shrinking in footprint, system designers must find innovative ways to package the electronics. Using 3-D IC packages is one technique that can help. For instance, cell phones often use memory stacked on top of baseband processors. Still, limited choices of 3-D techniques are currently available, so research giant IMEC (Interuniversity Microelectronics Center, Leuven, Belgium), is teaming with Icos Vision Systems in a program focusing on inspection and metrology for 3-D packaging.

Researchers will work at IMEC's laboratories, and Icos will provide technology and equipment for inspection and metrology. The joint-research program will concentrate on the development and optimization of several 3-D-packaging processes for ICs, including WLP (wafer-level packaging), flip-chip packages, SIPs (systems in packages), and MEMS (microelectromechanical systems) and on the optimization of the 3-D-metrology methods for these applications. IMEC is also hosting an affiliation program on 3-D stacked ICs, and the new program will complement that effort.

-by Maury Wright

- Icos Vision Systems, www.icos.be.

- ►IMEC, www.imec.be.

# It's the 8-bit entry point into a whole new world of opportunity.

### **Welcome to the Controller Continuum**

8-bit solutions from Freescale lead you into the Controller Continuum: our roadmap for 8-bit and 32-bit compatibility. This major expansion of our 8-bit portfolio—from 1K Flash to 128K Flash and from 6 pins to 122 pins—delivers not only unprecedented

choice and value, but the ability to scale in all directions from the low to high end. But we're not stopping there. With the Controller Continuum, we'll be rolling out pin-for-pin compatible devices. You can upgrade 8-bit designs to 32-bit performance and share the same set of peripherals and tools, such as the now easier-to-use Fast Track services for the CodeWarrior® tool suite. Now the applications you develop will not only be smarter, how you develop them will be too.

### BY HOWARD JOHNSON, PhD

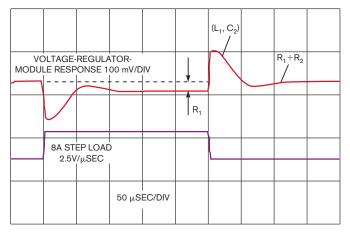

### Voltage-regulator model

love switching-regulator modules. They are efficient, you can configure them for many uses, and you can easily model them.

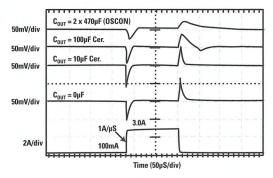

Figure 1 shows a typical characterization test for a regulator module—a Texas Instruments PTH08T220W switching-regulator module. The module is subject to an 8A step load, with a maximum dI/dt of 2.5V/µsec. The plot shows the load current at the bottom and the voltage-regulator response to this current at the top.

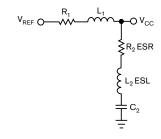

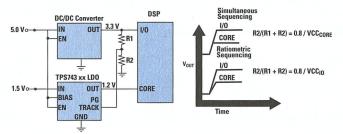

To build a circuit model for this voltage regulator, you need no additional information about the insides of the regulator. The step-response test reveals enough information to form a simple circuit model (Figure 2). The circuit model assumes a perfect voltage source,  $V_{\text{REF}}$ , connected through components  $R_1$  and  $L_1$  to your  $V_{\text{CC}}$  plane. Components  $R_1$  and  $L_1$  represent the action of the regulator.

Component  $C_2$ , along with  $R_2$  and  $L_2$ , represent the bulk capacitor (or array of bulk capacitors) in your application.

If, by looking at the data sheet, you can discover values for  $R_1$  and  $L_1$ , then you can build a circuit model such as the one in **Figure 2** for any application of the regulator.

The most straightforward parameter in this circuit is  $R_1$ . Over a time period of more than 100 µsec, the circuit comes to rest at a steady-state dc operating condition. After that time, capacitor  $C_2$  draws no appreciable steady-state current, so you may replace it with an open circuit. Similarly, replace inductor  $L_1$  with its dc equivalent: a short. The only operative component remaining in the circuit is resistor  $R_1$ , which directly controls the output droop, or steady-state dc offset. The value of  $R_1$  equals the ratio of droop to load current.

Over a medium scale of time, components  $C_2$  and  $L_1$  come into play, creating a damped sinusoidal response. The application note for this compo-

Figure 1 Four parameters control the low-frequency step response.

nent shows a typical step-response waveform with 1200  $\mu$ F of output capacitance. Given that data point, you just set  $C_2$  equal to 1200  $\mu$ F and adjust  $L_1$  to match the width of the sinusoidal glitch. Now you know  $L_1$ !

Last, given  $R_1$ ,  $C_2$ , and  $L_1$ , adjust  $R_2$  until you match the damping factor of each sinusoidal pulse. Now you know what ESR (equivalent series resistance) that manufacturer used when it snapped the step-response picture.

This simple circuit mimics the performance of the regulator at frequencies from dc to approximately 100 KHz. Above that range, the ESL (equivalent series inductance) of capacitor  $C_2$  comes into play, but this low-speed stepresponse test doesn't provide enough information to determine  $L_2$ . For a low-speed model, just leave  $L_2$  at zero.

This simple circuit model works for any voltage regulator with dominantpole feedback, meaning that the regulator does not use a multipole phasecompensating feedback structure. (Most don't.)

Always follow the manufacturer's guidelines for minimum capacitance and minimum ESR in your output capacitors. Failure to do so can produce unstable oscillations in the feedback circuit, destroying your circuit. Figure 2 does *not* model that aspect of regulator behavior.**EDN**

Figure 2 Most voltage regulators behave like this simple circuit.

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com or e-mail him at howie03@sigcon.com.

Echelon's power line technology is hassle-free: just plug it in, turn it on, and you're done. Field-proven in over 30 million devices around the world, our technology works reliably on <u>any</u> AC, DC, or unpowered circuit.

- ✓ Dual-channel BPSK modulation

- ✓ Low overhead forwarded error correction

- ✓ DSP-based noise cancellation and distortion correction algorithms

- ✓ Signal-to-noise ratio >80dB

- ✓ VA supply receive current 350µA typical

- $\checkmark$  Amplifier transit current 1Ap-p into 0.9 $\Omega$

- ✓ On-board application CPU

- ☑ SPI host interface

- ☑ RoHS-compliant 38TSSOP and 64LQFP IC packages

- ✓ Operating temperature -40 to +85°C

- ✓ DSK with Gerber files

- ✓ Open standard ANSI 709 based design

- Compliant with FCC, CENELEC, Industry Canada, Japan MPT regulations

Discover the technology that millions of devices worldwide already use. Call 1 408 938 5200 or visit us online at www.echelon.com/easyPL.

### **HP-IB** revolutionized ATE: Designers benefited from smarter connected instruments

he article that Hewlett-Packard contributed to EDN in 1972 describing an instrumentation bus didn't even mention HP-IB (Hewlett-Packard Instrument Bus). But, as the photo confirms, the article was the clear precursor to the HP-IB interface that competitors later dubbed the GPIB (General Purpose Interface Bus) and that ultimately became

the IEEE-488 interface. HP defined the bus both to allow instruments to communicate among themselves and to host computers or even calculators. Read the complete archived article on our Web site, and you'll find that the developers of the bus realized how valuable data dumps to a computer could be and how important the specification of a standard communication protocol would be in addition to the standardized physical interface.

The IEEE-488 interface became ubiquitous in the test-and-measurement industry by the late 1970s. HP and others even used the interface to connect computer peripherals, such as disk drives and monitors. Although the

ATE (automatic-test-equipment) segment may have been the biggest beneficiary of the bus, design engineers also gained more capable and intelligent instruments largely due to the prolific IEEE-488 standard.

The interface was also a precursor to backplane-centric test systems, such as PXI (PCI extensions for instrumentation), and even to the trend toward virtual instruments based largely on Intel-processor-based PCs. Engineers still widely use the IEEE-488 bus, although it is giving way in many applications to technologies such as PXI and virtual instruments. But the IEEE-488 concept may live a lot longer, because an industry group is developing the LXI (LAN-extensions-for-instrumentation) standard to move to an Ethernet-based alternative.**EDN**

### Digital bus simplifies instrument-system communication

INTERCONNECTING PROGRAMMABLE INSTRUMENTS INTO A TEST SYSTEM IS A FORMIDABLE TASK, HERE'S A RUNDOWN ON THE CONSIDERATIONS INVOLVED. AND A BUSING SCHEME THAT DOES THE JOB.

Donald C Loughry, Hewlett-Packard Co

Effective communication between two instruments, as in human communication, requires two essential elementsa good talker and a good listener. The design and use of instrumentation systems usually require many such communication links, or interfaces, as commonly termed. The practical implementation of these interfaces is not always easy.

Recognition of the fact that interface design involves much more than visible elements of cables, connectors, and circuits in the exchange of digital messages between instruments is of critical importance. All too often it is assumed

that agreement on physicalhardware requirements will achieve compatibility. Circuit compatibility, perhaps, but that is only part of the picture. The scope of the messages to be communicated, the unambiguous definition

of message content, and the techniques for exchanging these messages within a communications network are all important. Factors such as codes, formats, control techniques, timing, logic conventions and software requirements cannot be overlooked. Effective communications via a digital-interface system must consider all of these parameters. What

then are some of the specific problem areas causing outright incompatibility or, at best, costly interface design?

MESSAGE TRAFFIC INCREASES: A few years ago, only the most frequently changed and easily programmed front-panel controls were candidates for remote control. Now, it is not unusual to have all the front-panel controls on an instrument available for digital remote program control, even those usually implemented by analog means, such as vernier controls.

STORAGE: Although the scene is changing, many products still do not contain storage capability on program-data input or basic-data output lines. The absence of storage places extra demands on the interface as well as on some of the system elements.

MESSAGE CONVENTION: Each digital message carried on the interface must have an assertion state or logic convention associated with it. This is no different than many other conventions in life. Who would want to drive on the right-hand side of the road in the UK?

The need for automatic measurements coupled with the availability of low-cost digital-device technology to do the job have reduced the interface problem significantly. What used to take literally tens of interface interconnections all demanding new input data throughout a measurement cycle now requires but a few lines providing data input much less frequently. The result: Smart instruments are now able to communicate in a higher-level language, simplifying the interface task.—EDN, Sept 1, 1972

# ANALOG edge<sup>ss</sup>

Expert tips, tricks, and techniques for analog designs

Vol. IV, Issue 7

# Improving Video Clock Generation in Modern Broadcast Video Systems

By Alan Ocampo, Applications Engineer

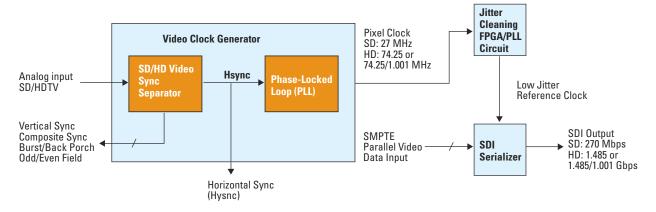

Figure 1. SDI Reference Clock Generator Block Diagram

he old adage "timing is everything" is well embodied in the modern broadcast studio, where precise timing of video clock and synchronization signals are essential to create, acquire, edit, and distribute analog and digital video. Today's broadcast systems must support industry-standard SD/HD formats, such as NTSC, PAL, 720p, 1080i, and 1080p, over analog and digital interfaces such as composite, component, and Serial Digital Interface (SDI). With high-speed SDI video equipment being increasingly used throughout the studio, improved video sync separation can more effectively produce video clocks with low jitter, which is crucial to meeting the stringent specifications of new SDI standards.

A video clock generator which generates various timing and clock signals from an analog video input consists of a video sync separator and Phase-Locked Loop (PLL). These two circuits are illustrated in the SDI application block diagram in *Figure 1*.

The video sync separator accepts a  $1V_{p-p}$  analog video input with bi-level or tri-level sync and extracts the standard timing signals, such as Horizontal (Hsync), vertical, and composite sync, burst/back porch, and odd/even field outputs. To meet strict timing requirements of the latest HDTV standards, specifications such as HD tri-level sync separation, low output propagation delay, and 50% sync slicing are imperative. The latter ensures precise sync extraction by slicing at the proper 50% point of the bi-level or tri-level sync reference edges. This provides for improved Hsync jitter performance compared to non-adaptive, fixed-level sync slicing, even under irregular input conditions such as double or no  $75\Omega$ load termination or transmission loss. Hsync jitter is defined here as the peak-to-peak time variance in Hsync's falling-edge with respect to the input's sync reference-edge and is critical to the performance of the pixel clocks generated by the subsequent PLL block.

### **NEXT ISSUE:**

**Powering Signal-Path Products**

### **Featured Products**

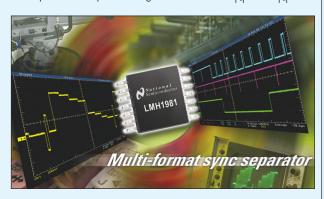

### **Multi-Format Video Sync Separator**

The LMH1981 is a multi-format sync separator for high-definition broadcast and professional video systems. The device automatically detects the input video format and performs all the necessary sync separation to generate low-jitter horizontal and vertical sync signals for standard and high-definition video formats, including NTSC, PAL, SECAM, 480i, 480p, 576i, 576p, 720p, 1080i, and 1080p.

The LMH1981 features the timing outputs needed for any video system, including horizontal, vertical and composite sync, odd/even field, burst/back porch clamp, and a patented automatic video-format detection feature. The device accepts both bi- and tri-level sync video inputs and features 50% slicing to ensure accurate separation of signals that vary in amplitude, offset, and noise. The device has a wide input range, allowing the inputs to accept video signals from 500 mV<sub>P-P</sub> to 2 V<sub>P-P</sub>.

### **Features**

- 50% sync slicing

- Low jitter horizontal sync output

- Supports NTSC, PAL, SECAM, 480i, 480p, 576i, 576p, 720p, 1080i, and 1080p

- Accepts video signals from 500 mV<sub>P-P</sub> to 2 V<sub>P-P</sub>

- No external programming with μC required

- Horizontal sync output propagation delay <50 ns</li>

The LMH1981 is ideal for use in a wide range of video applications such as, broadcast video equipment, video distribution, DTV and HDTV systems, and is available in TSSOP-14 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMH1981.html

### **Adaptive Cable Equalizer**

The LMH0044 adaptive cable equalizer is a monolithic integrated circuit for equalizing data transmitted over cable (or any media with similar dispersive loss characteristics). The equalizer operates over a wide range of data

rates from 143 Mbps to 1.485 Gbps and supports SMPTE 292M, SMPTE 344M, and SMPTE 259M. This device implements DC restoration to correctly handle pathological data conditions (DC restoration may be bypassed for low data rate applications). The equalizer may be driven in either a single-ended or differential configuration.

Additional features include separate carrier detect and output mute pins which may be tied together to mute the output when no signal is present. A programmable mute reference is provided to mute the output at a selectable level of signal degradation.

### **Features**

- SMPTE 292M, SMPTE 344M, and SMPTE 259M compliant

- High data rates: 143 Mbps to 1.485 Gbps

- Equalizes up to 200m of Belden 1694A at 1.485 Gbps or up to 400m of Belden 1694A at 270 Mbps

- 208 mW typical power consumption with 3.3V supply

- Manual bypass and output mute with a programmable threshold

- Single-ended or differential input

- Supports DVB-ASI at 270 Mbps

- 50Ω differential outputs

- Single 3.3V supply operation

The LMH0044 is ideal for SMPTE 292M/344M/259M serial interfaces, serial digital data equalization and reception, and data recovery equalization. The LMH0044 is available in LLP-16 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMH0044.html

### Improving Video Clock Generation in Modern Broadcast Video Systems

The PLL block can generate one or more pixel clocks, which should be phase-locked to the leading-edge of Hsync, the PLL's reference input. To produce both SD and HD pixel clocks will require two PLLs, both designed to give the appropriate output frequency for any given Hsync frequency. Since the PLL derives a higher frequency pixel clock from a lower frequency Hsync, pixel clock jitter will be determined by different sources at different frequencies. Below the loop bandwidth, the clock jitter output by the PLL will be dominated by Hsync jitter, which can be a significant amount depending on the performance and quality of the sync separator. Above the loop bandwidth, it will be dominated by its PLL oscillator, typically a Voltage-Controlled Crystal Oscillator (VCXO) chosen properly for low phase noise and frequency tuning, among other characteristics.

In the block diagram, a pixel clock generator is used to derive a reference clock for an SDI serializer which receives SMPTE-compliant parallel digital video data and then encodes, serializes, and transmits uncompressed serial digital video over coax cable. A serializer requires a clean reference clock for its internal PLL to generate a bit rate clock that maintains the serializer and clocks its output bit-stream. If used to directly clock the serializer, any jitter on the reference clock could potentially transfer to the bit rate clock and consequently appear as SDI output jitter. As shown in *Table 1*, SDI formats use increasingly high data rates and thus require clock sources with sufficient jitter performance.

For example, SMPTE 292M specifies the "timing" and "alignment" jitter requirements for an HD-SDI serializer's output bit-stream. Referring to the table, timing jitter should not be more than 1.0 UI¹ for jitter frequency components from B1 to B3, or 10 Hz to 1485 MHz, per SMPTE 292M. Alignment jitter—which is the high-frequency subset of timing jitter—should be no more than 0.2 UI from B2 (100 kHz) to B3. Outside of their respective frequency limits, both the timing and alignment jitter specifications roll

off at 20 dB per decade. Output jitter above the jitter specifications can result in degradation of error performance at the SDI deserializer. Please see the SDI standards for more information.

The stringent jitter specifications of SDI standards demonstrate the profound need for a low-jitter pixel clock. In most cases, however, a generated pixel clock will have an intolerable amount of jitter, up to 6 ns<sub>p-p</sub> for a typical SD pixel clock, which precludes direct application as a reference clock. Jitter reduction is therefore required to improve such unacceptable clock performance. The most common way to reduce pixel clock jitter is to use jitter-cleaning circuitry, usually implemented with additional Field-Programmable Gate Array (FPGA) or PLL stages. While jitter-cleaning circuitry is routinely applied by system designers, this can add significantly to component count, PCB area, power, and design cost and time.

A more effective way to reduce pixel clock jitter and thus improve SDI output jitter is to use a broadcast-quality video sync separator that has very low Hsync jitter, such as the LMH1981. This improved performance gives designers the flexibility to use smaller FPGAs or otherwise reduce jitter-cleaning circuitry and still produce an SDI output that complies to the jitter specifications.

Although broadcast systems are rapidly transitioning to high-speed SDI formats, the need to generate accurate video clocks from analog sources to process digital video data will be around for years to come. Current solutions require extensive jitter-cleaning circuits for generating an accurate reference clock to produce a SMPTE-compliant SDI output. However, the most fundamental and effective solution is to minimize jitter on the most critical timing reference, Hsync. This can only be accomplished using a high-performance analog video sync separator such as the LMH1981 in the clock generation signal path because, as we now know, timing is everything.

Access interactive broadcast video solutions diagrams at solutions.national.com

Table 1

| Format                                          | Standard         | Bit Rate                         |                                  | Output Alignment Jitter               |

|-------------------------------------------------|------------------|----------------------------------|----------------------------------|---------------------------------------|

|                                                 |                  |                                  | (B1 to B3)*                      | (B2 to B3)*                           |

| SD-SDI Standard- definition                     | SMPTE 259M, 334M | 270 Mbps, others not widely used | 1.0 UI¹ or 3.7 ns <sub>p-p</sub> | 0.2 UI or 740 ps <sub>p-p</sub>       |

| HD-SDI High-Definition;<br>HD/SD-SDI Mulit-rate | SMPTE 292M       | 1.485 Gbps<br>1.485/1.001 Gbps   | 1.0 UI or 673 ps <sub>p-p</sub>  | 0.2 UI or 135 ps <sub>p-p</sub>       |

| 3-Gbps SDI up to 1080p/60 over a single link    | SMPTE 424M       | 2.970 Gbps<br>2.970/1.001 Gbps   | 2.0 UI or 673 ps <sub>p-p</sub>  | 0.3 UI maximum,<br>0.2 UI recommended |

<sup>\*</sup>B1, B2, and B3 are the jitter frequency band limits specified in the SMPTE standards. One UI, or Unit Interval, is equal to one bit period (1/bit rate) of the serial bit-stream.

### **Featured Products**

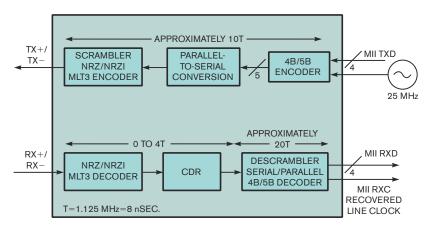

### Digital Video Serializer with Ancilliary Data FIFO and Integrated Cable Driver

The LMH0030 is a monolithic integrated circuit that encodes, serializes, and transmits bit-parallel digital video data. The serial data clock frequency is internally generated and requires no external frequency setting, trimming, or filtering components. The LMH0030 performs functions which include: parallel-to-serial data conversion, SMPTE standard data encoding, NRZ to NRZI

data format conversion, serial data clock generation and encoding with the serial data, automatic video rate and format detection, ancillary data packet management and insertion, and serial data output driving.

### **Features**

- SDTV/HDTV serial digital video standard compliant

- Supports 270 Mbps, 360 Mbps, 540 Mbps, 1.4835 Gbps, and 1.485 Gbps SDV data rates with auto-detection

- Low output jitter: 85 ps (typ), 125 ps (max)

- Low power consumption: 430 mW (typ) from 3.3V

- No external VCO required

- Fast PLL lock time: < 150 µs (typ) at 1.485 Gbps

- LVCMOS compatible data and control inputs and outputs

- $75\Omega$  ECL-compatible, differential, serial cable-driver outputs

- 3.3V I/O power supply and 2.5V logic power supply operation

The LMH0030 SDTV/HDTV serial-to-parallel digital video interfaces for video cameras, VTRs, telecines, digital video routers and switchers, digital video processing and editing equipment, video test pattern generators and digital video test equipment, and video signal generators. The LMH0030 is available in TQFP-64 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMH0030.html

### Digital Video Deserializer / Descrambler with Video and Ancillary Data FIFOs

The LMH0031 is a monolithic integrated circuit that deserializes and decodes SMPTE 292M, 1.485 Gbps (or 1.483 Gbps) serial component video data, to 20-bit parallel data with a synchronized parallel word-rate clock. It also deserializes and decodes SMPTE 259M, 270 Mbps, 360 Mbps, and SMPTE 344M (proposed) 540 Mbps serial component video data, to 10-bit parallel data. Functions performed by the LMH0031 include clock/data recovery from the serial data, serial-to-parallel data conversion, SMPTE standard data decoding, NRZI-to-NRZ conversion, parallel data clock generation, word framing, CRC and EDH data checking and handling, Ancillary Data extraction, and automatic video format determination.

### **Features**

- SDTV/HDTV serial digital video standard compliant

- Supports 270 Mbps, 360 Mbps, 540 Mbps, 1.483 Gbps, and 1.485 Gbps serial video data rates with auto-detection

- Low power: 850 mW (typ)

- Uses 27 MHz crystal or clock oscillator reference

- Fast VCO lock time: < 500 μs at 1.485 Gbps</p>

- Built-in self-test and video test pattern generator

- LVDS and ECL-compatible, differential, serial inputs

- 3.3V I/O power supply and 2.5V logic power supply operation

The LMH0031 SDTV/HDTV serial-to-parallel digital video interfaces for video editing equipment, VTRs, standard converters, digital video routers and switchers, digital video processing and editing equipment, video test pattern generators and digital video test equipment, and video signal generators. Operating over the commercial temperature range (0°C to +70°C), the LMH0031 is available in TQFP-64 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMH0031.html

### Low-Side Gate Driver ICs from 2A to 14A

Next Generation IXD\_5XX Low-Side Gate Drivers With Improved Cost-Efficiency, Circuit Density and Ruggedness for MOSFETs and IGBTs

### **Features**

- Diverse choice of single and dual outputs, with extensive mix of logic, packaging and output currents

- Enable options for fast, controlled shutdown

- Rated for operation from 4.5V to 35V and -55°C to +125°C

- Multiple packaging options, including high density 6-Lead DFN and 8-Lead DFN (4mm x 5mm)

- No internal cross conduction, output rise and fall times of 25ns maximum

### **Applications**

- Industrial Inverters, Motor Drives, Welding

- Consumer LCD TV, Audio Amplifiers

- Power Conversion SMPS, UPS, PFC

- Actuators Relays, Solenoids

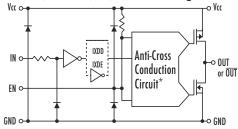

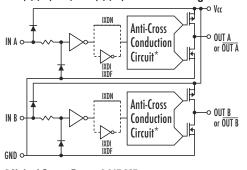

### IXD(D,E)509, IXD(D,E)514 Block Diagram

### IXD(I,N)509, IXD(I,N)514 Block Diagram

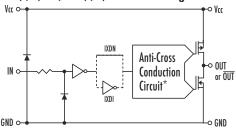

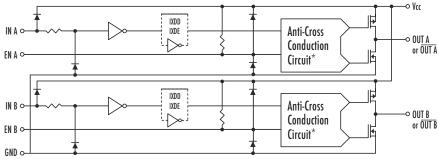

### IXD(F,I,N)502, IXD(F,I,N)504 Block Diagram

\* United States Patent 6,917,227

| Summary Tables for IDX_5XX Low-Side Gate Driver Family |                                         |                        |                            |  |  |  |

|--------------------------------------------------------|-----------------------------------------|------------------------|----------------------------|--|--|--|

| Part Numbers and Configurations                        |                                         |                        |                            |  |  |  |

| Part Number                                            | I <sub>PK</sub> @ T <sub>C</sub> = 25°C | Logic Configuration(1) | Package(2)                 |  |  |  |

| IXD(1)502(2)                                           | 2 A, Dual                               | F, I, N                | PI, SIA, SIAT/R, D1, D1T/R |  |  |  |

| IXD(1)504(2)                                           | 4 A, Dual                               | F, I, N                | PI, SIA, SIAT/R, D1, D1T/R |  |  |  |

| IXD(1)504(2)                                           | 4 A, Dual                               | D, E                   | PI, SIA, SIAT/R, D2, D2T/R |  |  |  |

| IXD(1)509(2)                                           | 9 A, Single                             | D, E, I, N             | PI, SIA, SIAT/R, D1, D1T/R |  |  |  |

| IXD(1)514(2)                                           | 14 A, Single                            | D, E, I, N             | PI, SIA, SIAT/R, D1, D1T/R |  |  |  |

| Logic Configurations                                   |                                         |                        |                            |  |  |  |

| Designation                                            | Configuration                           | Designation            | Configuration              |  |  |  |

| D                                                      | Non-Inverting + Enable                  | I                      | Inverting                  |  |  |  |

| E                                                      | Inverting + Enable                      | N                      | Non-Inverting              |  |  |  |

| F                                                      | Non-Inverting and Inverting             |                        |                            |  |  |  |

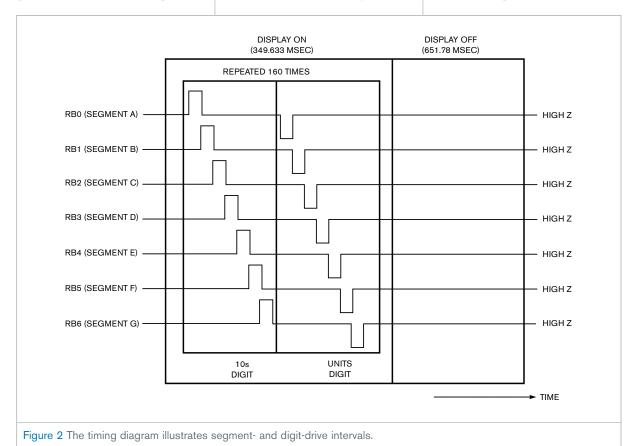

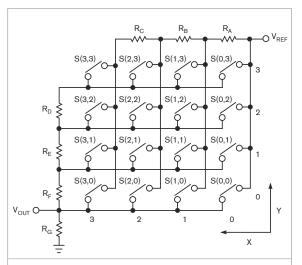

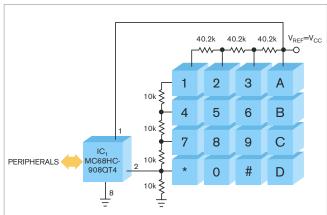

| Package Details                                        |                                         |                        |                            |  |  |  |